Intel touts Knights Corner 1 teraflop performance

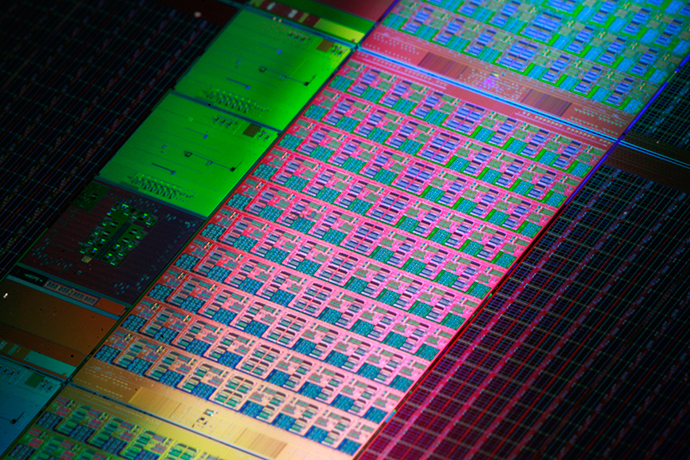

New accelerator chip based om Many Integrated Core architecture breaks the one-teraflop barrier

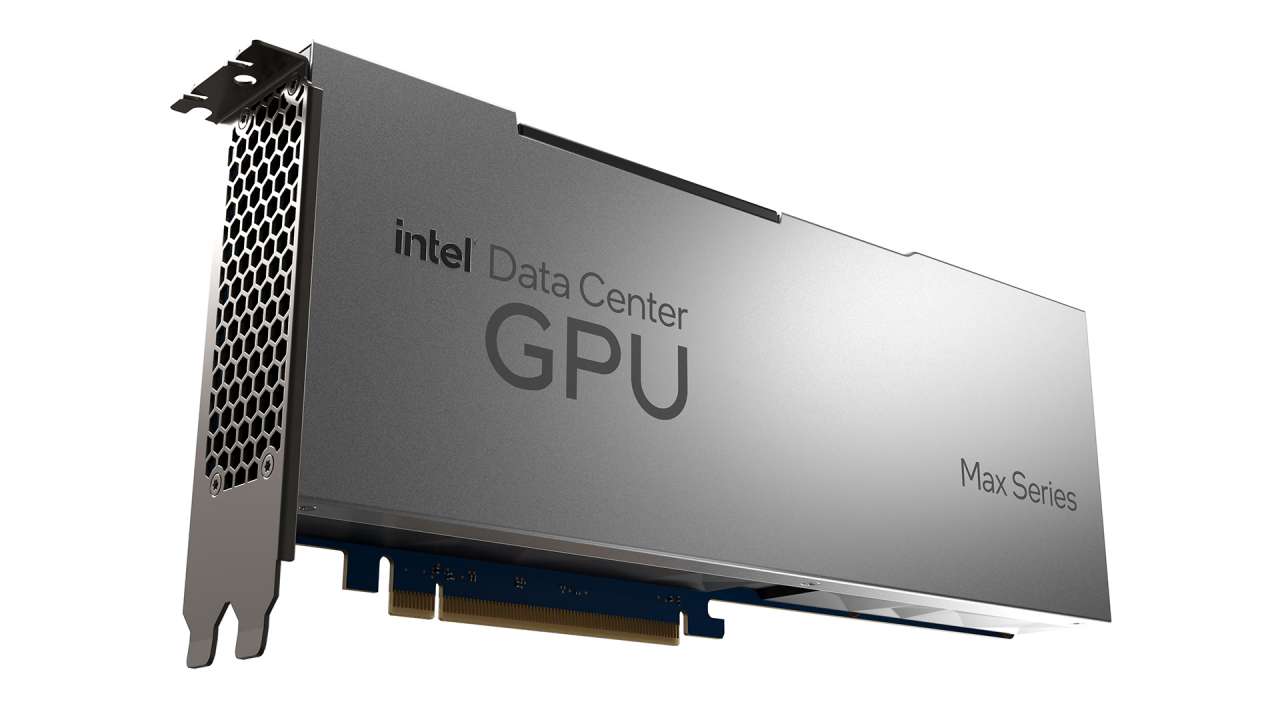

Intel yesterday showed off its first commercial co-processor to break the one-teraflop (TFLOP), or one trillion calculations per second, performance barrier.

Its Knights Corner accelerator chip, based on the Intel Many Integrated Core (Intel MIC) architecture, demonstrated its 1 TFLOP performance running on a test two-socket Xeon server at the Supercomputing conference in Seattle.

Intel said the exhibit reiterated its commitment to delivering efficient and programming-friendly platforms for highly parallel applications in high-performance computing (HPC) tasks, such as weather modelling, tomography and advanced materials simulation.

Having this performance now in a single chip based on Intel MIC architecture is a milestone that will once again be etched into HPC history.

Rajeeb Hazra, Intel general manager of technical computing and its connected systems group, said the first demonstration of a Teraflop supercomputer was in 1997 and used 9,680 Intel Pentium Pro processors as part of Sandia Lab's "ASCI RED" system at a cost of $55 million (34.9m).

"Having this performance now in a single chip based on Intel MIC architecture is a milestone that will once again be etched into HPC history," he said.

The chipmaker said Knights Corner will be manufactured using its 3D Tri-Gate 22nm transistor process and feature more than 50 cores. It did not, however, offer any more detailed specifications.

Get the ITPro daily newsletter

Sign up today and you will receive a free copy of our Future Focus 2025 report - the leading guidance on AI, cybersecurity and other IT challenges as per 700+ senior executives

Hazra added that the Knights Corner chip could be accessed and programmed as though it were a functional HPC compute node, unlike traditional graphic processing unit (GPUs) accelerators.

This enables it to be visible to applications as though it were a computer running its own Linux-based operating system (OS) independent of the host OS.

Targeting highly parallel processing workloads and existing x86 programming models and tools, its new performance level was measured using the Double-precision, General Matrix-Matrix multiplication (DGEMM) benchmark.

The Intel MIC architecture is designed to eliminate the need to port the code to a new programming environment in order to run existing applications.

This capability will allow scientists to use both CPU and co-processor performance simultaneously with existing x86-based applications, saving time, cost and resources that would otherwise be needed to rewrite them to alternative proprietary GPU languages, according to Intel.

The chipmaker said it already had a customer for a 10-petaflop system running its Knights Corner co-processor on PCI-Express processor slots, which will begin installation next year. The system, for the Texas Advanced Computing Centre, is expected to become fully operational in 2013.

A 25-year veteran enterprise technology expert, Miya Knights applies her deep understanding of technology gained through her journalism career to both her role as a consultant and as director at Retail Technology Magazine, which she helped shape over the past 17 years. Miya was educated at Oxford University, earning a master’s degree in English.

Her role as a journalist has seen her write for many of the leading technology publishers in the UK such as ITPro, TechWeekEurope, CIO UK, Computer Weekly, and also a number of national newspapers including The Times, Independent, and Financial Times.

-

Cleo attack victim list grows as Hertz confirms customer data stolen

Cleo attack victim list grows as Hertz confirms customer data stolenNews Hertz has confirmed it suffered a data breach as a result of the Cleo zero-day vulnerability in late 2024, with the car rental giant warning that customer data was stolen.

By Ross Kelly

-

Lateral moves in tech: Why leaders should support employee mobility

Lateral moves in tech: Why leaders should support employee mobilityIn-depth Encouraging staff to switch roles can have long-term benefits for skills in the tech sector

By Keri Allan

-

Accelerating business modernization

Accelerating business modernizationModernizing your infrastructure with the right servers can accelerate business transformation, enhance security, and future-proof your organization for tomorrow’s challenges

By Rene Millman

-

Intel layoffs to hit 15,000 roles as falling revenue and poor returns on AI bite

Intel layoffs to hit 15,000 roles as falling revenue and poor returns on AI biteNews CEO Pat Gelsinger announced news of the Intel layoffs following a recent earnings call

By George Fitzmaurice

-

Sustainable business starts with sustainable IT infrastructure

Sustainable business starts with sustainable IT infrastructureWhitepaper Reduce energy consumption without sacrificing performance with Intel and CDW

By ITPro

-

Winning the data-centric digital business in this decade

Winning the data-centric digital business in this decadeWhitepaper Discover more about Dell’s adaptive, secure, and resilient portfolio for the digital business and win in this data-centric era

By ITPro

-

Intel and Dell secure deal to build a digital twin of a UK fusion power plant

Intel and Dell secure deal to build a digital twin of a UK fusion power plantNews The simulation will be critical for meeting the ambitious goal of delivering fusion energy to the UK’s energy network in the 2040s

By Richard Speed

-

Continuously modernize storage

Continuously modernize storageWhitepaper Modernize data storage to accelerate operations and digital business initiatives

By ITPro

-

Why the likes of Shopify are bringing web designers to an end

Why the likes of Shopify are bringing web designers to an endOpinion Modern tools like Shopify are letting small businesses create viable sites for a fraction of the price it might have once cost

By Jon Honeyball

-

Intel pitches new 4th Gen Xeon chips as its "most sustainable" data centre processors

Intel pitches new 4th Gen Xeon chips as its "most sustainable" data centre processorsNews The chip giant suggested the launch of the 4th Gen Sapphire Rapids processors marks a turnaround in its recent history

By Bobby Hellard