IBM reveals road map to 5nm processor

Architecture crams in 30 billion transistors on chip as small as a fingernail

IBM has partnered with GlobalFoundries and Samsung to develop a manufacturing process that paves the way for 5nm chips.

In less than two years since developing a 7nm test node chip with 20 billion transistors, scientists have switched from using FinFET architecture to using stacks of silicon nanosheets as the device structure of the transistor.

Scientists working as part of the IBM-led Research Alliance at the SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex in Albany, NY achieved the smaller chip by using stacks of silicon nanosheets as the device structure of the transistor, instead of the standard FinFET architecture, which is the blueprint for the semiconductor industry up through 7nm node technology.

IBM said that the silicon nanosheet transistor demonstration, as detailed in the Research Alliance paper Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET, and published by VLSI, "proves that 5nm chips are possible, more powerful, and not too far off in the future".

It added that compared to the 10nm technology available in the market, a nanosheet-based 5nm technology can deliver 40% performance enhancement at fixed power, or 75% power savings at matched performance.

It said the work is first in the industry to demonstrate the feasibility to design and fabricate stacked nanosheet devices with electrical properties superior to FinFET architecture.

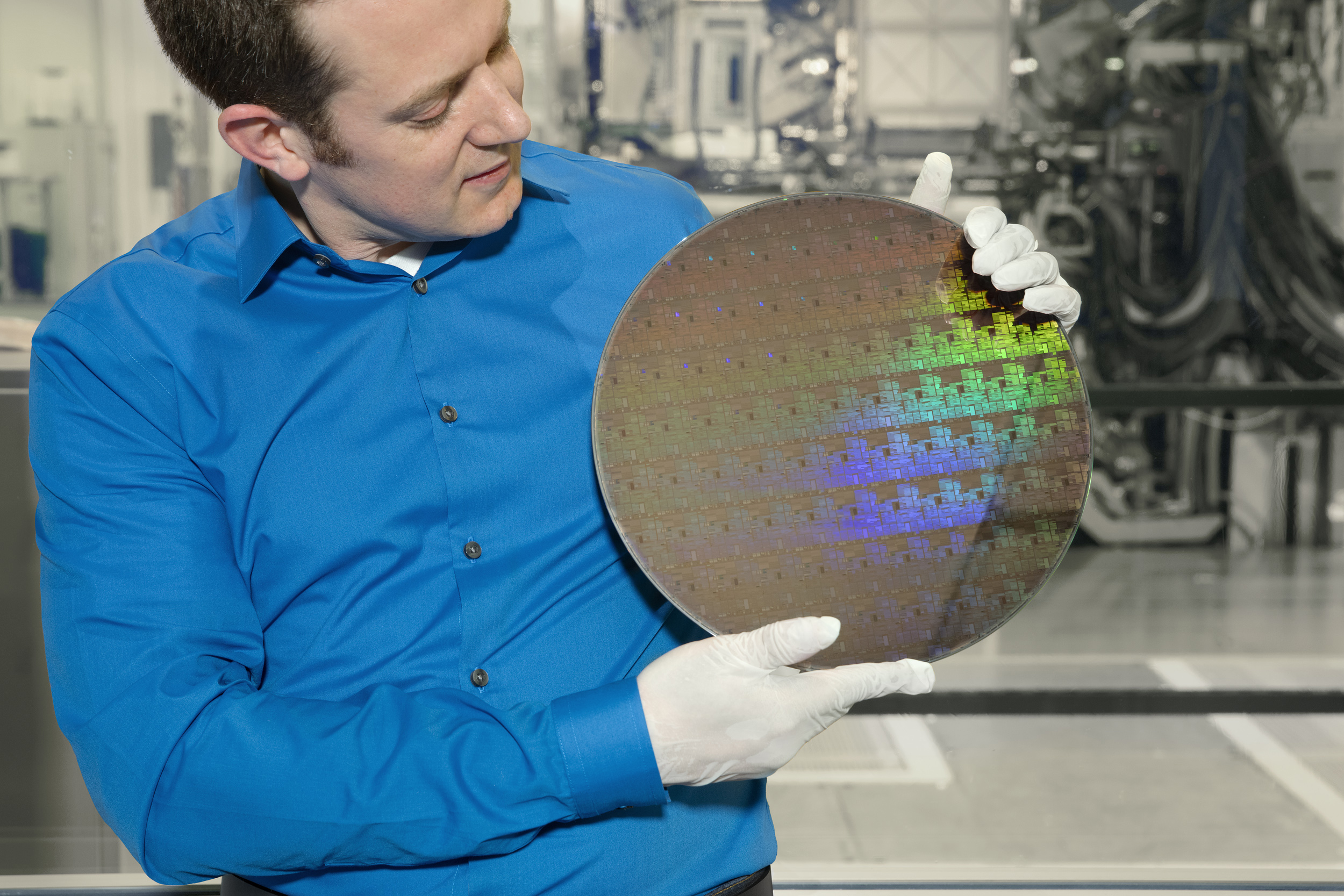

According to IBM, this same Extreme Ultraviolet (EUV) lithography approach used to produce the 7nm test node and its 20 billion transistors was applied to the nanosheet transistor architecture. Using EUV lithography, the width of the nanosheets can be adjusted continuously, all within a single manufacturing process or chip design.

Get the ITPro daily newsletter

Sign up today and you will receive a free copy of our Future Focus 2025 report - the leading guidance on AI, cybersecurity and other IT challenges as per 700+ senior executives

This adjustability permits the fine-tuning of performance and power for specific circuits something not possible with today's FinFET transistor architecture production, which is limited by its current-carrying fin height. Therefore, while FinFET chips can scale to 5nm, simply reducing the amount of space between fins does not provide increased current flow for additional performance.

IBM said the resulting increase in performance will help accelerate cognitive computing, the Internet of Things (IoT), and other data-intensive applications delivered in the cloud. The power savings could also mean that the batteries in smartphones and other mobile products could last two to three times longer than today's devices, before needing to be charged.

"For business and society to meet the demands of cognitive and cloud computing in the coming years, advancement in semiconductor technology is essential," said Arvind Krishna, senior vice president of Hybrid Cloud, and director at IBM Research.

"That's why IBM aggressively pursues new and different architectures and materials that push the limits of this industry and brings them to market in technologies like mainframes and our cognitive systems."

Dr. Bahgat Sammakia, Interim President at the SUNY Polytechnic Institute, said that this 5nm transistor is a "significant milestone for the entire semiconductor industry as we continue to push beyond the limitations of our current capabilities."

Rene Millman is a freelance writer and broadcaster who covers cybersecurity, AI, IoT, and the cloud. He also works as a contributing analyst at GigaOm and has previously worked as an analyst for Gartner covering the infrastructure market. He has made numerous television appearances to give his views and expertise on technology trends and companies that affect and shape our lives. You can follow Rene Millman on Twitter.

-

The UK government wants quantum technology out of the lab and in the hands of enterprises

The UK government wants quantum technology out of the lab and in the hands of enterprisesNews The UK government has unveiled plans to invest £121 million in quantum computing projects in an effort to drive real-world applications and adoption rates.

By Emma Woollacott Published

-

Netgear WBE710 review

Netgear WBE710 reviewReviews The compact WBE710 delivers great cloud management features and a good turn of Wi-Fi 7 speed – but it does have a premium price tag

By Dave Mitchell Published